This makes me borderline giddy… I fucking love it!

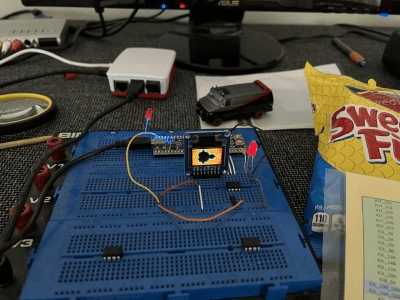

Here’s a project that demonstrates the advantage of having an opensource instruction set (RISC-V) along with the power of being able to wire an FPGA into one. This project implements a minimal RISC-V core in an iceFUN FPGA board. While having a license-free instruction set is nice, it also opens up the possibility to implement custom instructions, in this case a Mandelbrot instruction. The video below demonstrates the speed improvement that can be gained by optimizing it in hardware with a custom instruction.

…

This shows why RISC-V and FPGAs can be important. RISC-V is completely opensource and anyone can obtain the PDF with the description of the instructions and implement anything they need. With other CPUs, a license would be need to be paid, but here RISC-V is free and open. The FPGA is like a stem-cell of microchips. The chip has a big grid of logic units and Verilog code can wire them together into… whatever. In this case it’s wired to be a RISC-V CPU. Since in this case, the mulw instruction (which is supposed to be a 64 bit multiply) is not being used, this project is using the opcode to compute Z = Z^2 + C for 16 iterations to compute Mandelbrot pictures:

https://www.mikekohn.net/micro/riscv_fpga.php

HT: https://hackaday.com/2024/01/17/compute-the-mandelbrot-set-with-a-custom-risc-v-cpu/

Leave a comment